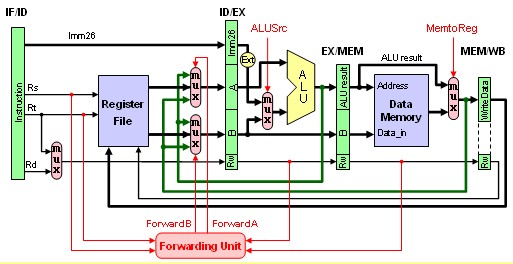

The following figure shows the forwarding unit in a pipelined datapath.

| The unit controls the ALU multiplexors to replace the value from a general-purpose register with the value from the proper pipeline register. It includes two tasks: |

|

- Generate two control signals

ForwardAandForwardB, which are used to control the two forwarding multiplexors, and - Use

RsandRtin IF/ID andRwin ID/EX and EX/MEM.

Consider the following instruction sequence:

lw $4, 100($9) # $4 = Mem[100+[$9]]

add $7, $5, $6 # $7 = $5 + $6

sub $8, $4, $7 # $8 = $4 - $7

When lw reaches the MEM stage, add will be in the ALU stage and sub will be in the Decode stage.

ForwardA=10 ⇒

Forward data from MEM stage and

ForwardB=01 ⇒

Forward ALU result from ALU stage.

|

|