- Structural Hazards

-

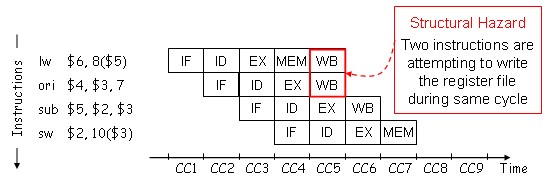

A structural hazard occurs when a part of the processor’s hardware is needed by two or more instructions at the same time.

For example,

Assume a datapath has a single memory instead of two. It is possible that in a clock cycle an instruction is accessing data from memory while another instruction is fetching an instruction from that same memory.

Without two memories, the pipeline could have a structural hazard. The figure below shows another example of a structural hazard where writing back the ALU result in Stage 4 conflicts with writing load data in Stage 5.

There are two ways to solve the structural hazard:

- Delay access to resource

- Include a mechanism to delay instruction access to resource. For example, delay all write backs to the register file to Stage 5. Therefore, the ALU instructions bypass Stage 4 (memory) without doing anything.

- Add more hardware resources (more costly)

- Add more hardware to eliminate the structural hazard. Redesign the register file to have two write ports. The first write port can be used to write back the ALU results in Stage 4 and the second write port can be used to write back load data in Stage 5.

|

The other day my girlfriend told me to take the spider out instead of killing it…. So we went out and had some drinks. He’s a cool guy, wants to become a web developer. |