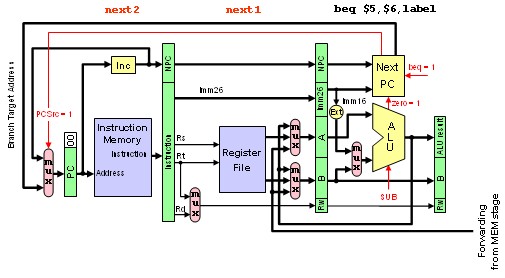

This slide shows how the hardware handles control hazards by stalling. Consider the following instruction sequence:

beq $5, $6, label

next1

next2

...

label: lw $8, 32($7)

The figure shows by the time the branch instruction reaches the ALU stage, the instruction next1 is in the decode stage and the instruction next2 is being fetched.

|

|

The

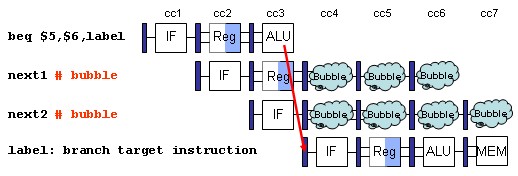

next1 through next2 instructions will be fetched no matter whether the branch is taken or not taken.

A common improvement over branch stalling is to assume that the branch will not be taken and thus continue execution down the sequential instruction stream.

If the branch is taken, the pipeline should flush next1 and next2.

Otherwise, they can be executed if branch is not taken.

Flush is to discard instructions in a pipeline by changing control values to 0s.

| The figure shows the branch is taken and two instructions following the branch are flushed. |

|